- 全部

- 默认排序

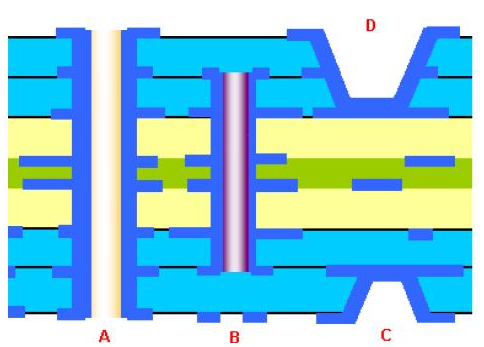

答:盲埋孔,是盲孔与埋孔的统称。盲孔(Blind vias ),盲孔是将PCB内层走线与PCB表层走线相连的过孔类型,此孔不穿透整个板子。埋孔(Buried vias),埋孔则只连接内层之间的走线的过孔类型,所以是从PCB表面是看不出来的。盲孔一般是激光钻孔,从表层钻到PCB的内层,并不穿透整个PCB板,激光钻孔的大小是0.1mm,厚度是60-70um左右,具体要看PCB厂家的工艺能力。所以我们在PCB设计软件中,设置的盲孔大小一般是4mil的钻孔,10mil的焊盘。埋孔,跟普通的钻孔所使用的钻

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

答:ICT,In Circuit Tester,自动在线测试仪,是印制电路板生产中重要的测试设备,用于焊接后快速测试元器件的焊接质量,迅速定位到焊接不良的引脚,以便及时进行补焊。在PCB设计中,就需要在设计中添加用于ICT测试的焊盘。ICT测试可以检测的内容有:线路的开短路、线路不良、元器件的缺件、错件、元器件的缺陷、焊接不良等,并能够并能够明确指出缺点的所在位置。一般来说,ICT常用的设计要求如下所示:Ø ICT测试点焊盘大小直径为40mil,最小不小于32m

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

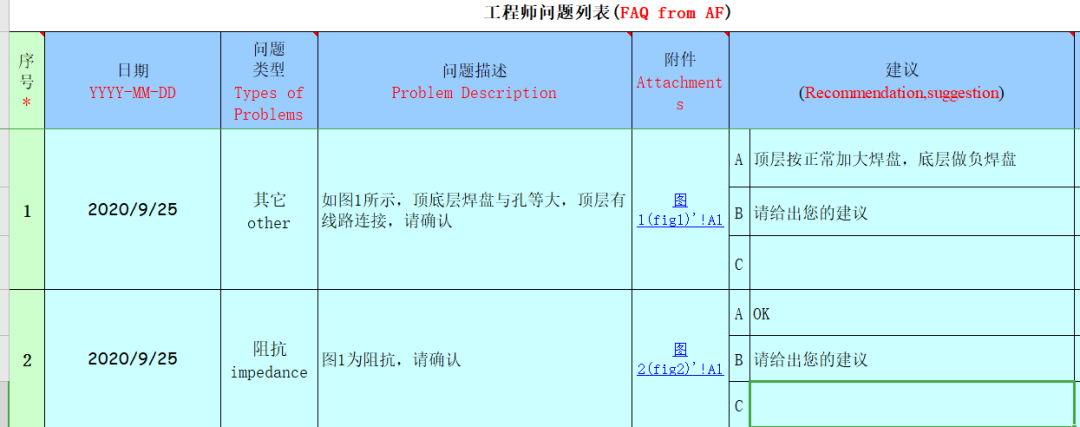

相信作为PCB设计工程师的我们都应该知道,每次设计完PCB设计发给板厂制板的时候,是不是经常会收到PCB板厂反馈回来的【EQ问询】,有些工程师对这类问题搞不懂,胡乱回复一通,做回来之后板子根本就没办法用,找板厂麻烦,板厂一句话可能回复你【我

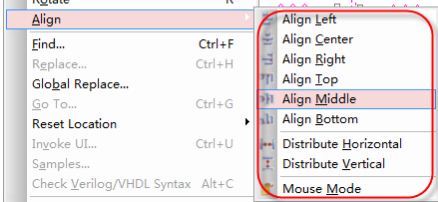

答:在使用Orcad软件绘制原理图的时候,为了使原理图绘制的美观一些,有时候也希望像PCB设计一样,将所有的器件都进行对齐,这里我们给大家介绍下,原理图器件对齐的方法,方便大家在原理图设计的时候也可以将元器件进行对齐。第一步,首先,我们在一张原理图上放置四五个电阻器件,如图3-205所示,一共是6个电阻,我们放置的时候都不是对齐的; 图3-205 电阻放置示意图第二步,框选需要对齐的器件,然后执行菜单命令Edit-Align,对齐的命令,如图3-206所示,就可以对元器件对

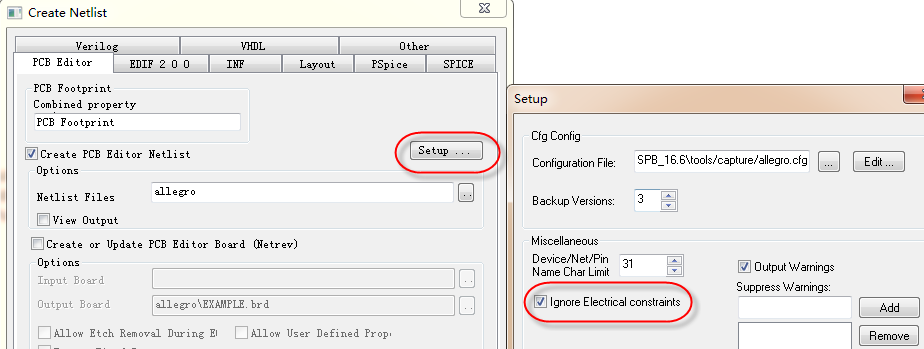

答:我们在进行PCB设计的时候呢,尽量不要把原理图的规则导入到PCB中,我们需要在输出网表的时候进行设置,具体的操作步骤如下所示:第一步,选中原理图的根目录文件即DSN文件,进行网表的输出,执行菜单Tools-Create Netlist,创建网表;第二步,在弹出的输出PCB网络表的对话框中,其它地方都是不用勾选的,在右侧有一个Setup选项,是输出网络的参数设置按钮,我们需要在这里进行不输出原理图规则的设置;第三步,点击输出网表的Setup选项,进行参数的设置,如图3-211所示,在左侧箭头所

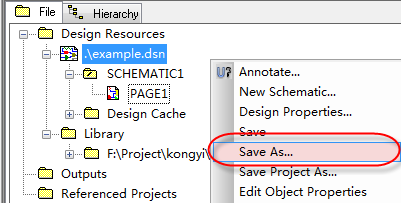

答:我们在进行原理图设计或者是进行PCB设计,都会遇到这样的问题,需要降低设计文件的版本,我们这里讲解下,Orcad软件设计的原理图如何去降低原理图的版本,操作的步骤很简单,我们这里列举一下操作的步骤:第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本; 图3-212 原理图另存低版本示意图第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的

扫码关注

扫码关注